2006.7.1作成

2007.10.5修正

2010.10.5追記

2016.4.17修正

井上 IC-200

| ☆周波数・モード | 非公開 |

| ☆定格出力 | 非公開 |

| ☆最大周波数偏移 | 非公開 |

| ☆送信周波数構成 | 非公開 |

| ☆受信周波数構成 | 非公開 |

| ☆マイクインピーダンス | 非公開 |

| ☆受信方式 | 非公開 |

| ☆受信感度 | 非公開 |

| ☆通過帯域幅 | 非公開 |

| ☆電源 | 非公開 |

| ☆消費電力 | 非公開 |

| ☆寸法・重量 | 非公開 |

| ☆発売年・定価 | 非公開 |

リグの説明

井上電機時代のアイコムが発売した100チャンネルのトランシーバです。

PLLトランシーバと記されていますが、現在のように発振周波数を低い周波数に変換してから分周・位相比較するのではありません。

低い周波数に変換後、別に水晶発振した周波数と位相比較しています。水晶発振子を20個も使用するぜいたくな構成です。

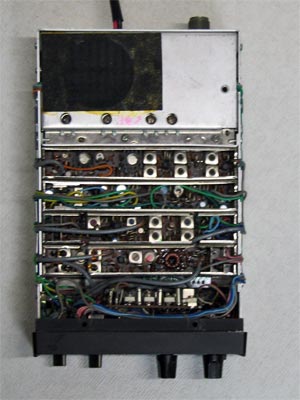

写真左側が11MHz台の水晶、右側(LO-1から10)が13MHz台の水晶です。

ブロックダイヤグラムを下に示します。

|

|

| 上面図 |

下面図 |

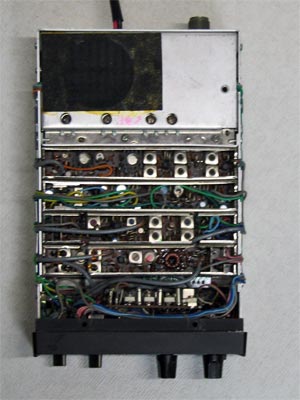

回路は各ブロック毎に分割され、本体にメジ止めしてからブロック間を配線しています。故障した場合、故障ブロックを交換すればメンテナンスが楽そうですが、ブロック間の配線がクセモノです。

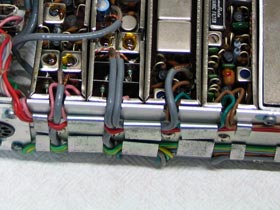

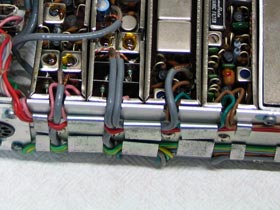

左下の写真をご覧下さい。これが側面です!ブロック間の配線は側面を通り、止め金具で固定します。上・下にコの字型のケースを取り付けますが、ケースと配線の隙間がほとんどありません。実は配線の一部の被覆が剥がれてしまい、応急処置をしています。

左下の写真をご覧下さい。これが側面です!ブロック間の配線は側面を通り、止め金具で固定します。上・下にコの字型のケースを取り付けますが、ケースと配線の隙間がほとんどありません。実は配線の一部の被覆が剥がれてしまい、応急処置をしています。

受信部

初期データはまあまあなので、更に良くなることを期待して調整を行いました。

高周波増幅入力のコイルは効果がありませんが、10.7MHzセラミックフィルタ出力のコイルを調整するとS1程度の向上がありました。455KHz増幅回路のコイル2個も少しメータが振れるようです。

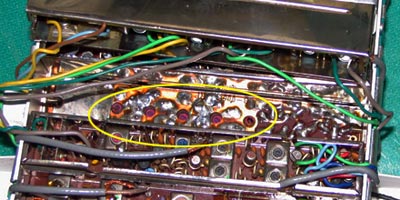

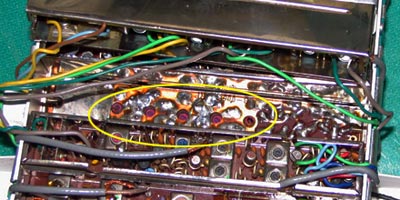

ヘリカルキャビティも調整出来ないか、と調べてみたら、裏の送信回路ブロックを外したら受信回路基板の裏に調整コア5個が見えました。(右写真のマルの箇所)

早速調整を・・・と思ったら、発振音がして止まりません。送信ブロックを取り付けると止まります。発振音は低周波回路の回りこみで調整には無関係と判断し、うるさいのを我慢して(Hi)コアを調整しました。ここでも改善効果が見られました。

また、受信帯域がワイドのままなので、455KHzのセラミックフィルタをCFM455CからCFM455Eに交換しました。ディスクリを調整し、ひとまず終了です。

調整後は、以下のような結果になりました。高い周波数で落ち込みがありますが、使用しない領域なので気にしないことにします。メータは2目盛り多く振れるようになりました。(メータは0から10までの均等目盛りで、S表示ではありません)

受信感度は、20dBNQ -6dB(F=145.00MHz)でした。

送信部

周波数が高くなると出力が低下します。145.0MHzで送信しながらトリマ・コイルを回して調整したら、バンド内の変化は残るものの最大12W出るようになりました。

ドライブ段はコイル2個あるいは4個の複同調があります。周波数の高い側と低い側でそれぞれ均一になるように調整しました。これでバンド内で均一に出力が得られました。

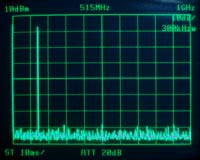

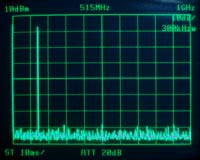

ところがスペアナで観察すると、送信周波数±10.7MHzで-60dBの近接スプリアスがありました。出力を低下させずに近接スプリアスが最小になるように複同調を再調整し、-65dB以下(ノイズレベル以下)にしました。

このような調整が出来、スペアナさまさまです。

2倍の高調波も-60dBぎりぎりクリアしました。

X:100MHz/div Y:10dB/div F=145.00MHz

送信周波数はPLL(133MHz)と水晶発振回路(10.7MHz)をミックスするので、それぞれ調整します。10.7MHzが1.3KHz低めだったので、誤差100Hz以下に調整しました。PLL出力の誤差は最大8KHzあったので、各発振出力をトリマで調整し誤差100Hz以下にしました。11MHz台の水晶はトリマが1個だけ手の入らないところにあります。設計上の難点ですが、面倒なのと誤差500Hz程度なのでOKとしましたHi。

(この調整は受信データを取得する前に実施しました)

ワイド機なので、デビエーション調整とマイクゲインの調整は必要です。これらはメーカー発表の資料に従って調整しました。

その他

回路をブロック毎に分けて構成する方法は本機以前のリグでも見られます(手持ちのIC-20で確認)。きれいに見えますし、故障箇所発見にはブロックを交換すれば良いので(基板をコネクタで差し替えるのと同じようなものです)手軽なのですが、反面ブロック単位で構成するためにパーツが増えてコストアップになります。

本機以降、徐々に基板1-3枚程度にまとめる設計に変更されています。トランシーバ設計の過渡期のセットとも言えるのではないでしょうか。

井上電機時代のアイコムが発売した100チャンネルのトランシーバです。

井上電機時代のアイコムが発売した100チャンネルのトランシーバです。

井上電機時代のアイコムが発売した100チャンネルのトランシーバです。

井上電機時代のアイコムが発売した100チャンネルのトランシーバです。

初期データはまあまあなので、更に良くなることを期待して調整を行いました。

初期データはまあまあなので、更に良くなることを期待して調整を行いました。

周波数が高くなると出力が低下します。145.0MHzで送信しながらトリマ・コイルを回して調整したら、バンド内の変化は残るものの最大12W出るようになりました。

周波数が高くなると出力が低下します。145.0MHzで送信しながらトリマ・コイルを回して調整したら、バンド内の変化は残るものの最大12W出るようになりました。 ところがスペアナで観察すると、送信周波数±10.7MHzで-60dBの近接スプリアスがありました。出力を低下させずに近接スプリアスが最小になるように複同調を再調整し、-65dB以下(ノイズレベル以下)にしました。

ところがスペアナで観察すると、送信周波数±10.7MHzで-60dBの近接スプリアスがありました。出力を低下させずに近接スプリアスが最小になるように複同調を再調整し、-65dB以下(ノイズレベル以下)にしました。